本文基本结构为:

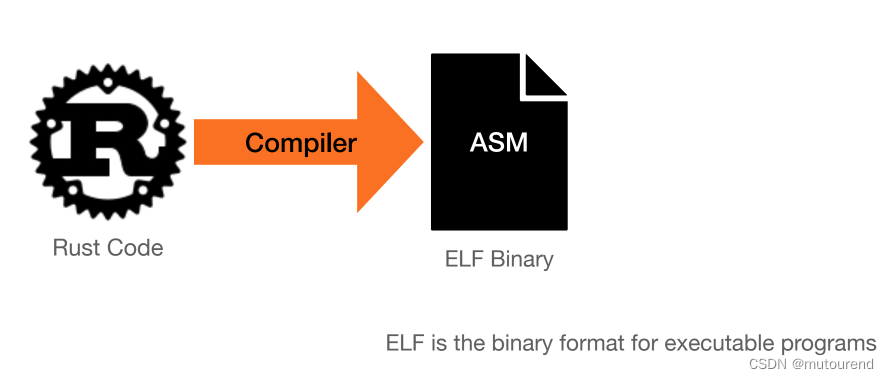

编程语言背景介绍RISC-V虚拟机作为zkVM电路为何选择RISC-V? 2. 编程语言背景介绍高级编程语言不专门针对某个架构,其便于人类编写。高级编程语言代码,经编译器编译后,会生成针对专门某架构的汇编代码,汇编代码是供机器使用的。

直接写汇编代码的好处之一是:

可对系统进行细粒度的控制。但汇编代码存在如下问题:

表达性有限专门针对特定机器难于维护而借助编译器,使用高级编程语言,可解决以上问题,如:

各种高级编程语言,经相应的语言后端,可生成相应的LLVM bytecode,然后经LLVM编译出特定机器架构的汇编代码:

何为RISC-V?:

RISC = Reduced Instruction Set ComputerV = This is UC Berkeley’s 5th RISC ISA(Instruction Set Architecture)具体的RISC-V说明书见:

The RISC-V Instruction Set Manual

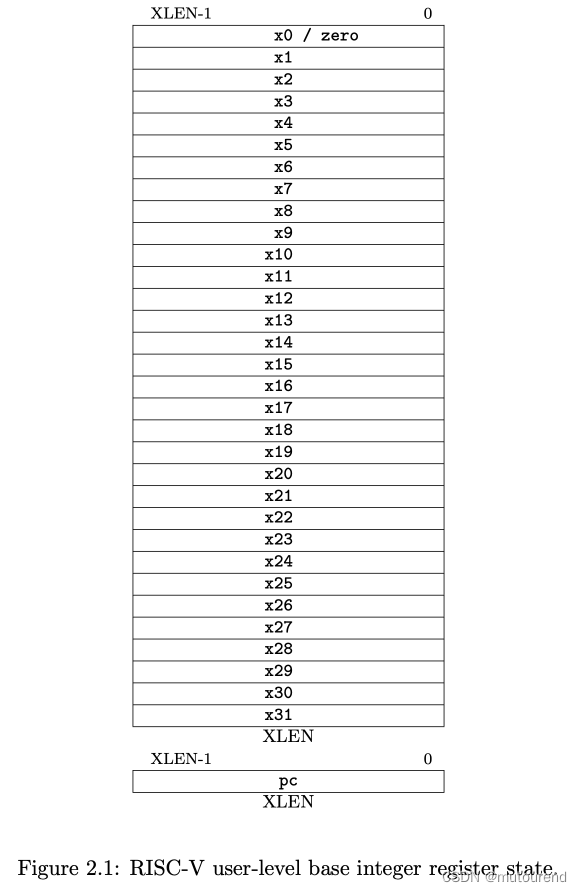

1)RV32I:Base整数指令集。每个寄存器为32位。有32个寄存器。【使用XLEN术语来表示x寄存器的宽度位数,如是32、64还是128。】

有31个通用寄存器x1-x32来保存整数值,x0寄存器固定为常数值0。

2)RV32E:Base整数指令集。每个寄存器为32位。为RV32I的子集,只有16个寄存器。

3)RV64I:Base整数指令集。每个寄存器为64位。

4)RV128I:Base整数指令集。每个寄存器为128位。

5)M:表示为对整数乘法和触发的标准扩展。以RV32M为例,其具有的指令集为:

RISC-V可实现为:

1)硬件芯片2)或 虚拟机:RISC Zero 将RISC-V用作虚拟机。

当将RISC-V用作虚拟机时,其:

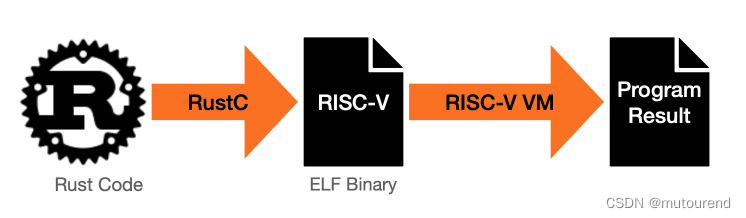

以软件来实现RISC-V寄存器和内存运行RISC-V指令 即,以程序代码编译后的RISC-V汇编代码(ELF二进制文件)作为RISC-V虚拟机的输入,经RISC-V执行,获得相应的程序结果。 3. RISC-V虚拟机作为zkVM电路zkVM的目的为:

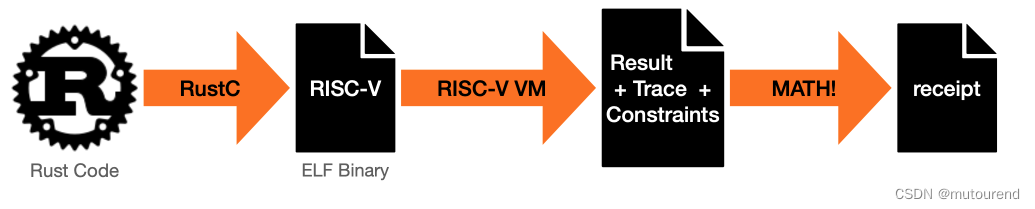

为程序执行生成receiptsRISC Zero zkVM的目的为:

为RISC-V程序执行生成receipts为生成receipt,需:

1)有RISC-V代码执行的execution trace2)有相应的一组约束,如: 每个bit应为 0或1:x * (x-1) = 0。每个寄存器应包含32位数据。每个指令执行完后,program counter应变化。 3)基于RISC-V虚拟机输出的程序结果 + execution trace + 约束,经某证明系统数学处理,生成相应的receipt。

实际在实现RISC-V虚拟机时,如何区分zkVM中所执行的是哪个程序代码呢?

答案就是Image ID。所谓Image ID,是加载到内存的ELF二进制的Merkle root。会将Image ID写入到seal中。

[1] RISC Zero团队2023年2月视频 What does RISC V have to do with RISC Zero’s zkVM【slide见What RISC-V has to do with RISC Zero’s zkVM】

[2] ARM新规,芯片行业震动丨X86、ARM、RISC-V和MIPS对比汇总

[3] The RISC-V Instruction Set Manual